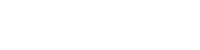

As advanced 2.5D and 3D IC packaging technologies require large capital expenditures for R&D and manufacturing capabilities, there will be only a few companies involved in this field, with ASE competing with TSMC, Intel, and Samsung Electronics.

Join tip3x on Telegram

According to Digitimes, the market for high-performance computing (HPC) chip solutions that require advanced packaging has been expanding and has a bright future. For example, suppliers including AMD and Nvidia have adopted TSMC’s CoWoS package in their HPC processors.

Moreover, ASE’s Silicon has the ability to provide packaging technology utilizing silicon bridges for HPC solutions, and its fan-out embedded bridge (FO-EB) is already competitive with silicon bridge products from Intel and TSMC, the sources said. The above-mentioned person said that ASE has cut into the supply chain of the first-class server chip company in the United States with its advanced packaging capabilities.

Furthermore, TSMC’s silicon bridge solution helped secure orders for Apple’s M1 Ultra SoC. TSMC said its CoWoS package is in its fifth generation, dubbed CoWoS-S, based on a silicon interposer three times the size of a reticle, with the flexibility to accommodate SoCs, Chiplets, and 3D stacks such as high-bandwidth memory.

Furthermore, TSMC’s silicon bridge solution helped secure orders for Apple’s M1 Ultra SoC. TSMC said its CoWoS package is in its fifth generation, dubbed CoWoS-S, based on a silicon interposer three times the size of a reticle, with the flexibility to accommodate SoCs, Chiplets, and 3D stacks such as high-bandwidth memory.

Both ASE and TSMC declined to comment on specific customers and orders.

Industry insiders further stated that obtaining sufficient high-end ABF substrates is also critical to a company’s advanced packaging capabilities. Advanced packaging technologies for high-performance computing devices, such as TSMC’s CoWoS and InFO_oS, and ASE’s FOCoS, require sourcing substrates from third-party suppliers.